Digital VHDL Lock

An exploration into digital system design: a VHDL-implemented lock utilizing a state machine for secure access control on a Basys3 FPGA board.

The Digital VHDL Lock project demonstrates the design of a secure system using state machines and flip flops, simulated and implemented on the Basys3 FPGA board with Vivado Software. The lock's operation, dictated by a specific button combination, is a testament to practical VHDL applications in security.

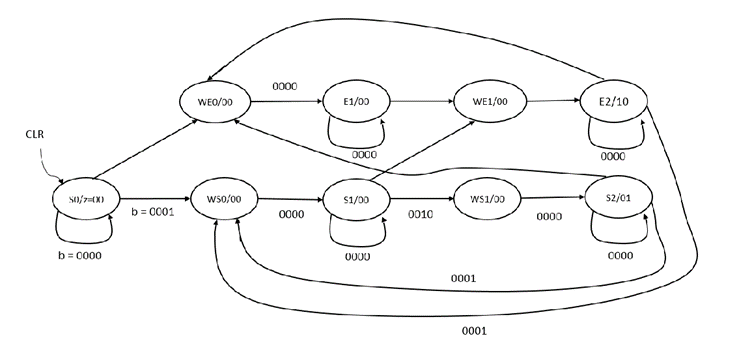

The project's core is a state diagram that outlines the lock's functionality. In its default state, the system awaits a correct input to transition to a secure state, while incorrect attempts lead to an error state, both visually represented by LEDs.

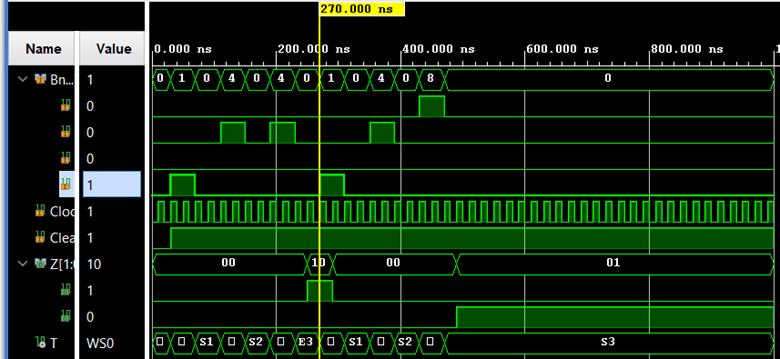

The Vivado simulation confirms the lock's behavior, displaying how the system reacts to input sequences. A correct sequence turns on the rightmost LED, indicating access granted, while an incorrect one triggers the leftmost LED, signaling denied access.

This lab's success in creating a functioning digital lock provided valuable insights into digital system design, deepening my understanding of VHDL and state machine concepts.